マイコン - ラッチアップ

概要

マイコンは膨大な数のPN接合で構成されており、その中には、PN接合が2つ連なった4重構造のPNPNが構成さている部分がある。

PNPNの構造は、電力用スイッチング素子として使用されるサイリスタの構造であり、マイコン内のPNPN部分は、寄生サイリスタと呼ばれる。

サイリスタは、アノードとカソードとゲートの3端子で構成され、通常アノードからカソードへ電流は流れないが、

ゲートに信号を入力すると、アノードからカソードに向かって電流が流れる。

1度、流れ始めた電流は、電源を切らない限り流れ続ける。

この時、オン抵抗は非常に小さいので、大電流が流れる。

これと同様の現象が、マイコンの中の寄生サイリスタで発生することを、ラッチアップと呼ぶ。

マイコンでラッチアップが発生すると、内部に大電流が流れて、正常に動作しないどころか、

最悪の場合、マイコン内部の配線の溶断、素子の破壊などを引き起こす。

正常な使用方法であれば、ラッチアップは発生しないが、

電源の立ち上げ手順を間違えたり、急峻な高電圧ノイズが端子に入った場合に発生する。

下図に、実際にラッチアップの電流で溶解したマイコン表面のメタル配線の写真を示す。

サイリスタ構造

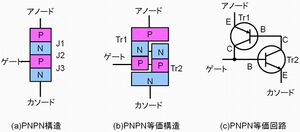

下図(a)にサイリスタ構造を示す。

アノードに正電位、カソードに負電位を印加した時、J1とJ3は順方向であるがJ2は逆方向であるので、アノードからカソードへ電流は流れない。

しかし、ゲートに電圧を印加して電流を流す時、J2の逆方向電流がゲート電流によって加速され、J2に電流が流れる。

J1とJ3は順方向であるので、この現象が発生すると、アノードからカソードに電流が流れる。

1度、電流が流れると、アノードの電源を切らない限り電流は流れ続ける。

これがサイリスタのスイッチング動作である。

この動作を利用して、サイリスタは電力用機器でスイッチング素子として使用される。

上図(b)のように、PNPN接合はPNP型トランジスタとNPN型の結合と考えられる。

回路図にすると、上図(c)のような2つのトランジスタの構成になる。

トランジスタTr1のエミッタが、サイリスタのアノードになる。

ベースは、トランジスタTr1のコレクタ(トランジスタTr2のベース)になる。

カソードは、トランジスタTr2のエミッタになる。

ラッチアップ発生のメカニズム

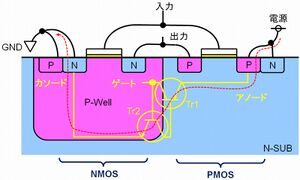

この2つのトランジスタをマイコンの中のCMOSに当てはめると下図のようになる。(N-SUB)

他に、P-SUBの場合もあるが、どちらの場合も寄生PNPN接合が形成されるので、ラッチアップの原理は同じように考えることができる。

電源に接続されているP-MOSのソースのPchからN-SUB、そしてP-WELLと続く経路でトランジスタTr1が形成される。

そして、N-SUBからP-WELL、GNDに接続されているNMOSのソースのNchの経路でトランジスタTr2が形成される。

トランジスタTr1とトランジスタTr2は、上図のCMOSの中で、黄線で描かれた様に形成されていることになる。

電源側がアノード、GND側がカソード、ゲートはN-MOSのP-WELLに相当する。

CMOSの入力ラインは、N-MOSのゲートに接続されており、ゲートとP-WELLは、ゲート酸化膜を挟んでコンデンサと同じ構造を形成している。

もし、入力ラインにノイズが入り、そのノイズのdV/dtが大きい場合(高周波成分が大きい場合)、コンデンサは高周波信号を通すので、

ゲート酸化膜を通り抜けてP-WELLに到達する。

そして、これがトリガーとなることにより、PNPN接合がオン状態になり、電源からGNDにかけて大電流が流れる。

また、電源が急峻に変動する場合(特にマイナス側に変動する場合)、

ゲート電圧が電源電圧よりも高くなり、ゲートにノイズが入ったのと同様の状態になる。

マイコンの電源を投入する前に端子に電圧を印加すると、この状態になる。

マイコンの内部において、PNPN接合は無数に存在するので、どのPNPN接合でラッチアップが発生するか不明である。

ラッチアップを引き起こす要因

ラッチアップを発生させる要因は、次のようなものがある。

- 端子から入る外乱ノイズ

- 外乱ノイズの立ち上がり / 立ち下がりが急峻でdV/dtが大きい場合、IC内部まで到達して、任意の場所のPNPN接合がオン状態になる。

- 一般的に、ノイズは電磁界によるノイズを指すが、静電気によって発生する高電圧もノイズとして考えられる。

- 電源から入るノイズ

- 電源にノイズが入り、電源の電位が低くなり、PNPN接合のゲートにノイズが入った時と同じ現象が起きて、ラッチアップは発生する。

- ICに電源が投入されていない状態で、端子に電圧を印加することも、この場合に当てはまる。

- 端子から外来ノイズを入れているのと同じ状態になる。

- IC内部の電圧変動により、ゲートにノイズと同じ現象が発生する場合

- IC内部に大きな電流が流れる場合、内部に電位差が発生して、PNPN接合のゲートにノイズが入った時と同じ現象が起きて、ラッチアップが発生する。

- 電源に大電流が流れる場合やGNDから大電流が流れる場合も、ラッチアップが発生する。

- 同様に、端子から大電流が流れる場合も、IC内部の電圧変動を引き起こして、ラッチアップが発生する。

対策

ラッチアップの対策において、上記のセクションで記載した要因を防ぐことである。

具体的には、次のような対策がある。

- 外乱ノイズを端子に入れない

- 外乱ノイズが多い環境でICを動作させる場合、ノイズが端子に入らないように遮断する。

- どうしてもノイズが入る場合は、ノイズのdV/dtを小さくする工夫が必要である。

- 例えば、シールド、制限抵抗、コンデンサ、フェライトコア等が有効である。

- 電源投入手順を守る

- ICによっては、複数の電源を持っているものがある。

- その場合、マニュアルに電源投入手順または電源投入時の注意事項が記載されていることがある。

- 必ず、マニュアルの手順を遵守して電源を投入する。

- 過大な電流を電源ラインや端子に流さない

- 過大な電流の目安は、絶対最大定格である。

- 電源や端子に絶対最大定格を超える電流を流すと、ICにダメージを及ぼすだけではなく、

- IC内部の電圧変動を引き起こして、ラッチアップの原因になる。

- 絶対最大定格は遵守する。

- 保護回路を設ける

- ラッチアップによりICに大電流が流れた場合、その電流を検知して、電源を遮断するする保護回路も有効である。

- ラッチアップによる大電流は、電源を切れば止まるので、保護回路があればICは破壊されない。