マイコンの基礎 - Octo SPI

概要

Octo SPIは、Quad SPIを8ビット拡張したパラレル通信機能である。

したがって、マイコンの基礎 - Quad SPIを先に読むことを推奨する。

2015年以降、さらに繊細なグラフィックや幅広いマルチメディア、多量のデータを必要とするコンテンツへの需要が高まってきたため、

Quad SPIよりもデータスループットを向上させたOcto SPIがマイコンに搭載されるようになった。

Quad SPIと同様、メモリマップドモードを使用すると、外部メモリに対して内部メモリのようにアクセスすることができる。

これにより、システムのバスマスタ(例:DMA等)は、CPUが停止している低消費電力モードでも外部メモリに自動的にアクセスすることができ、

モバイルアプリケーションやウェアラブルアプリケーションにおいて、外部メモリのアクセス効率をさらに向上させることができる。

このページでは、STマイクロ社のSTM32L4+シリーズに搭載されているOcto SPIを例にして記載する。

下図に、STマイクロ社のSTM32L4+シリーズに搭載されているOcto SPIを示す。

Octo SPIの特長

Octo SPIインタフェースを使用すると、

マイコンは外部のSingle SPI(通常のSPI)、Dual SPI、Quad SPI、Dual Quad SPI、Octo SPIのメモリと通信することができる。

Octo SPIで接続されるメモリは、メモリ空間上にマッピングされているため、マイコンは内部メモリと同様にアクセスでき、読み出しや書き込みを行う。

わずか数本のピンで外部メモリを簡単に接続できることが大きな特長である。

これにより、Flash ROMやRAM等の外部メモリを簡単に増設することができる。

Octo SPIインタフェースは、1つのデータレーンから最大8つのデータラインまで、あらゆるSPIメモリに対応するフレームフォーマットの構成である。

Quad SPIと同様、設計者は各フェーズの有効化 / 無効化、各フェーズの長さの設定、各フェーズで使用するライン数の設定(1~8)を行うことができる。

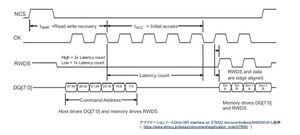

下図のように、RWDS信号は、書き込み時にはライトストローブとして、読み出し時にはリードクオリファイとして機能する。

ハードウェアインタフェース

インタフェースは、次の信号ラインで構成される。

- チップセレクト用

- OCTOSPI_nCSライン

- クロック用

- OCTOSPI_CLKライン

- OCTOSPI_nCLK

- データストローブ用

- OCTOSPI_DQSライン

- データ用

- OCTOSPI_IO[0~7]ライン

クロックやチップセレクト信号ラインは、基本的にどの場合でも同じであるが、データラインの扱いは異なる。

Quad SPIとして使用する場合は4レーンのみ使用、Octo SPIとして使用する場合は8レーン使用する。

Dual Quad SPIとして使用する場合は8レーンを2つに分けて、それぞれを2つのQuad SPIメモリに接続する。(下図を参照)

プロトコル

Octo SPIインタフェースは、2つの異なるプロトコルで動作することができる。

- レギュラーコマンドプロトコル

- シングルエンドクロック : 3.3[V]信号

- HyperBusプロトコル

- 差動クロック : 1.8[V]信号

各プロトコルは、インダイレクトモード、自動ステータスポーリングモード、メモリマップドモードの3つの動作モードをサポートしている。

レギュラーコマンドプロトコル

レギュラーコマンドプロトコルは、Octo SPIがコマンドを使用して外部メモリと通信する基本的なフレームフォーマットであり、

各コマンドは、最大5つのフェーズを含むことができる。

対応可能な外部メモリは、Single SPI、Dual SPI、Quad SPI、Dual Quad SPI、Octo SPIのメモリである。(下図を参照)

HyperBusプロトコル

HyperBusプロトコルは、HyperRAMやHyperフラッシュメモリと通信するプロトコルである。(下図を参照)

HyperBusは、ダブルデータレートインタフェースを採用しており、1クロック当たり2つのデータバイトがDQ入出力信号を介して転送されるため、

高いスループットの読み出しや書き込みが可能である。

フレームは、コマンド / アドレスフェーズ(以下、CAと呼ぶ)とデータフェーズの2つのフェーズで構成される。

CA期間中、OCTOSPI_DQSラインはリードライトデータストローブ(以下、RWDSと呼ぶ)として使用され、追加の初期アクセスレイテンシを挿入する必要があるかどうかを示す。

CA期間中にRWDSがLowである場合、1つのレイテンシーカウント(以下、tACCと呼ぶ)のみが挿入される。

また、Highである場合、追加で2倍のtACCが挿入される。

tACCは、データが転送される前に初期レイテンシー要件を満たすために使用され、データ転送のないクロックサイクル数を表す。

特定のクロック周波数に必要な初期レイテンシーカウントはデバイスに依存し、HyperRAMのコンフィギュレーションレジスタで定義される。

Hyperフラッシュメモリの場合、RWDSはリードデータストローブとしてのみ使用される。

動作モード

動作モードには、インダイレクトモード、自動ステータスポーリングモード、メモリマップドモードの3種類がある。

- インダイレクトモード

- 通常のSPIと同じモード(読み出し / 書き込み / 消去操作)のことである。

- HyperBusプロトコルやレギュラーコマンドプロトコルは問わない。

- CPUやDMAを用いて、Octo SPIのデータレジスタを介して行う全ての操作に対応している。

- また、外部メモリデバイスの設定にも使用できる。

- 自動ステータスポーリングモード

- メモリのステータスレジスタをハードウェアで完全に管理する自動ポーリングが可能である。

- この機能により、ソフトウェアのオーバーヘッドやソフトウェアによるポーリングが不要となる。

- ポーリングの結果が一致した場合は、割り込みを発生させることもできる。

- メモリマップドモード

- 外部メモリに対して、あたかもメモリマップに割り当てられた内蔵メモリのようにアクセスできるモードである。

- また、外部メモリからコードを実行することもできる。(下図を参照)

図. 外部メモリマッピング